Capacitor Reduction

By Christopher Halford Advanced Layout Solutions Ltd

The humble multi-layer ceramic capacitor, the ‘MLCC’, is an unlikely candidate for grabbing industry headlines, but they have recenly been doing just that. Oddly, despite being ubiquitous and an important component in any electronic device, they are becoming increasingly hard to procure.

It is estimated that annual production of MLCCs sits at around 1 trillion pieces per year, making them an unlikely sounding candidate for scarcity. However, production has not significantly grown in recent years and is not expected to do so in the very near future. Compare that with the continual growth in demand and suddenly the problem is obvious. The era of connecting everything electronically has led to an explosion in the ownership of (regularly replaced) tech gadgets. Although you’re unlikely to give it a moment’s thought, we move around with an extraordinary number of MLCCs about our person.

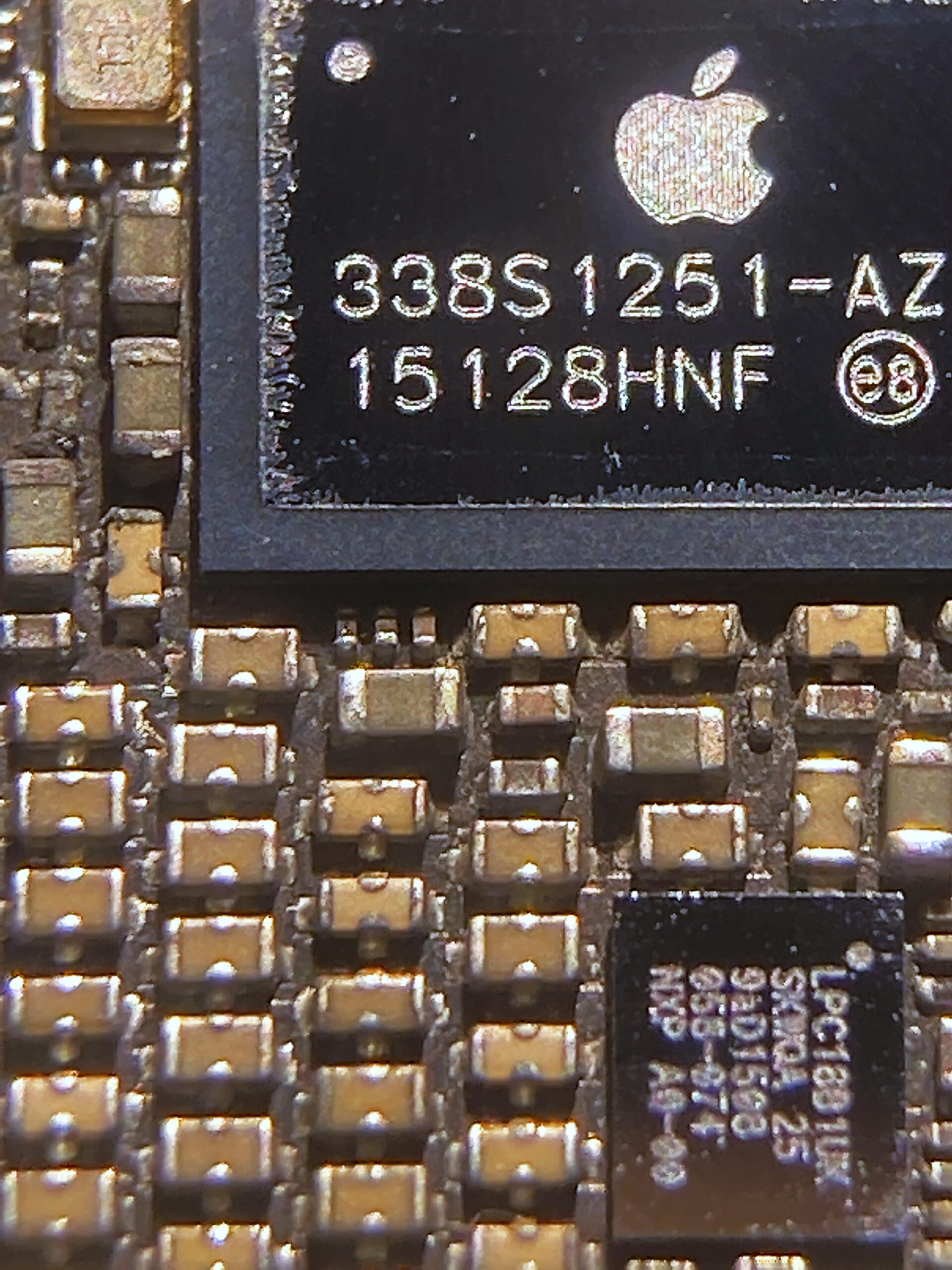

MLCCs – in Apple’s iPhone 6

An iPhone 6, for example, contains ~700 MLCCs. This figure increases to >1,000 in the iPhone X. A new internal combustion engine’d car may contain >2,500 MLCCs, whereas a TESLA swallows up >10,000 pieces.1 The punchline is, whether we know it or not, we are all using many more MLCCs than ever before without much increase in production, leading to inevitable shortages, increased prices and long delivery times.

Why Do We Use Them?

Electronic devices require the ‘local’ distributed capacitance that MLCCs provide in order to minimise noise and prevent supply voltages from sagging during load transients. The goal is to design a power delivery network (PDN) that can provide sufficiently large surges of current when required, without the voltage dropping at the load. MLCCs form a vital part of this PDN and are therefore required to help provide a suitably low impedance between power and ground at the ICs.

Do We Really Need Them?

Most of them, probably. Maybe. We know they’re needed (designers don’t add >1,000 components to a smartphone for fun) but how many to add presents a whole new design challenge.

In the absence of an appropriate design methodology various ‘rules-of-thumb’ are adopted by engineers when adding capacitors to a design. One example is the ‘one capacitor per power pin’ rule. This rule serves as a reasonable guide when an IC package has just a very few power/ground pins and where the capacitors can be placed close to those pins. However, if the rule is applied to BGAs with many hundreds of balls it can quickly become ridiculous. IC package designers tend to tie-off unused balls to the power and ground supplies rather than leave them unused. It is therefore not uncommon to see hundreds of MLCCs added to a design for this reason, without any chance of the parts being fitted even remotely close to their intended ICs.

Another common approach that uncertainty can promote is to add multiple MLCCs of decade value spacings in the hope that this lowers the plane impedance across a wider frequency range (e.g. each site contains 1uF, 100nF, 10nF, 1nF, 100pF…). Unsurprisingly, ‘scatter-gun‘ approaches such as these have been a recipe for excessive parts being added to designs and is causing component purchasers a big headache today.

In the past these components have been seen as cheap and readily available and so, when designing a quality product, designs have been ‘seasoned’ with plenty of extra MLCCs for good measure, without too much thought for whether or not they are necessary. We know that the law of diminishing returns applies and, at some point, there will be no performance benefit in adding further MLCCs.

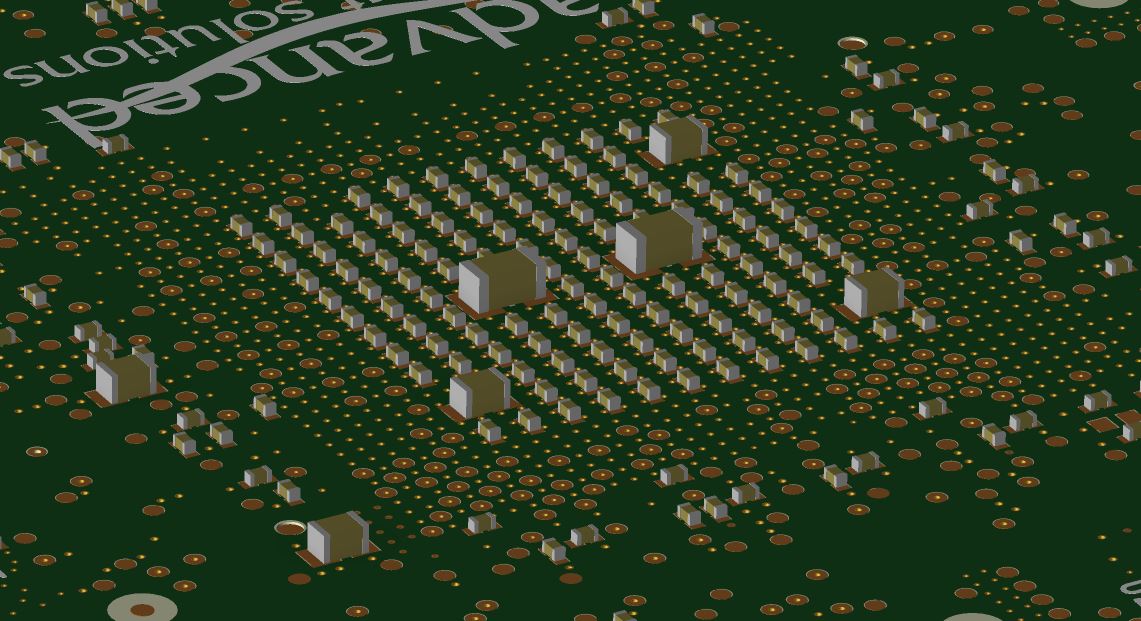

Array of Small MLCCs Located Under a Large GPU

A Better Approach – Impedance Simulation

In order to make informed decisions and select a more optimal capacitor scheme, the power delivery network can be modelled through power-integrity analysis. High-quality S-parameter and SPICE model libraries are readily available from capacitor vendors such as muRata, Kemet and AVX. These behavioural models are combined with the PCB structure (copper shapes, voids, dielectrics, vias, traces, etc.) to create a detailed model of the entire PDN.

It is now fairly common for IC vendors to specify the impedance profiles required for the voltage rails of larger processors. This profile describes the maximum impedance permitted across frequency as seen by the processor. Additionally, package models may also be supplied that further model the effects of on-board capacitors, the impedance requirement then being measureable at the die itself. Through iterative ‘what-if’ simulation, the PDN can then be explored to understand which capacitors are actually required. Poorly placed small capacitors will typically give no benefit whatsoever to the impedance of a PDN. If that is the case, they simply cost money to place on the PCB, eat up board space and cause procurement difficulties.

To date, we have found that our capacitor reduction simulations usually demonstrate that a significant number of capacitors are redundant and not providing much benefit to the PDN. The simulations often also reveal that whilst capacitors may be further lowering the impedance, the figure being achieved is far lower than required and the PDN is, in essence, being over-engineered.

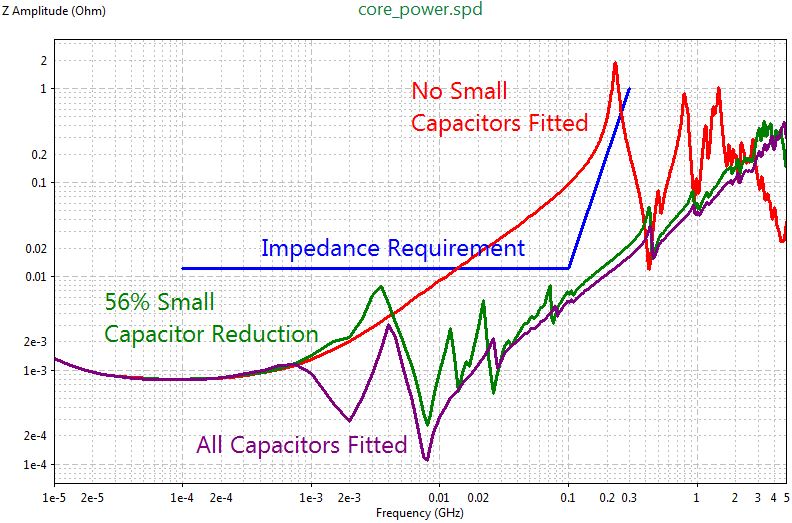

The plot below shows an example impedance requirement mask of <12mOhms up to 100MHz. With no small capacitors near the processor this mask is violated at frequencies just over 10MHz (red curve). The purple trace shows that with all capacitors fitted the design easily satisfies the impedance mask. However, iterative simulations showed that 56% of these small capacitors could be removed from the design whilst still providing reasonable headroom to the impedance mask (green curve). The impedance is clearly ‘worse’ but is completely acceptable.

Impedance of Capacitor Schemes

Conclusion

In the short-term there is no end in sight to the component shortages that the industry is currently experiencing. Using power integrity analysis on system PDNs can provide valuable evidence that some MLCCs can be rationalised, or even completely removed from a design. Designers of high-volume products have been conscious of this for a long time in order to keep costs down. However, the issue is now just as relevant for low-volume designs, and even one-off prototypes and technology-demonstrators in order to avoid component availability woes.

For more information on capacitor

simulations, please contact:

Advanced Layout Solutions Ltd

Fronds Park, Frouds Lane, Aldermaston,

Reading, Berkshire, RG7 4LH, UK

1 Figures published by Kemet

http://www.signalintegrityanalysis.com

Tel: +44 (0) 118 971 1930

©2021 Advanced Layout Solutions Ltd